AMD developed the technology in collaboration with TSMC, who manufacture critical CCDs with gen computing cores and GPUs for AMD. DSMC already has a number of 3D packaging technologies, and AMD now seems to be making use of this portfolio. In a subdivision, Dr. Lisa Su said it will also be used for future HPC products. The Milan-X looks as real as the Raison processors with 3D V-cache.

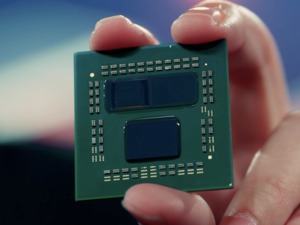

According to AMD, it is a prototype of a Raisen 5000 processor with an additional SRAM of 64 MB per CCD. Since AMD decided to make a variant with two CCDs for the prototype, we come up with the 2x 32MB L3cache that was already in the CCDs and add the new 3D V-cache 2x64MB.

The 3D V-cache is connected directly to the CCD via DSV (through Silicon Via) using 3D packaging technology. The data rate of this connection is more than 2 TB / s. The so-called “structural silicon” creates a high part where there is no 3D V-cache, so that the height of the CCD is again the same.

In the renderings of the 3D V-cache or the new Gen-3-CCD with this memory, it can be seen that the L3-cache is otherwise located above the surface of the CCD. Areas where gen 3 cores are located are left on the other side. This prevents the 3D V-cache from covering hot cores. Structure Silicon ensures that the cores are coated for heat dissipation.

In the keynote address, Lisa Su held a prototype in front of the camera. This is a Raison 5000 processor with two CCDs. However, to prove the difference, only one CCD had a 3D V-cache (left).

Processors or caches provided can then be imagined as:

| L3-cache | 3D V-cache | Total | |

| Raison 9 5950X | 64 MB | . | 64 MB |

| Risen 9 5950X with 3D V-cache | 64 MB | 128 MB | 192 MB |

| Raison 9 5900X | 64 MB | – | 64 MB |

| Raison 9 5900 X Mid 3D V-Cache | 64 MB | 128 MB | 192 MB |

| Raison 9 5800X | 32 MB | – | 32 MB |

| Raison 9 5800 X Mid 3D V-Cache | 32 MB | 64 MB | 96 MB |

| EPYC 7763 | 256 MB | – | 256 MB |

| EPYC 7763 with 3D V-Cache | 256 MB | 512 MB | 768 MB |

The Raison processor with two CCDs brings it 128 MB of V-cache and a total of 192 MB L3 cache. It has 64 MB in addition to the total 96 MB with a CCD. With the EPYC processors, the Milan-X should then be very similar, we are only talking about different cache sizes here. An EPVC processor with eight CCDs already has a 256 MB L3 cache. The 3D V-cache comes with an additional 512 MB of functionality, so we are talking about a total of 768 MB. You can see in what form AMD equips its Raison and EPOC processors with 3D V-cache.

To demonstrate the benefits of 3D V-Cache, AMD provided a benchmark. The Gears 5 ran once with the Raison 9 5950X and once with the 3D V-cache emulator 12 cores. Both processors worked at a constant clock rate of 4 GHz. While the Raison 9 5950X has reached 184 fps, the Raison processor with 3D V-cache has reached 206 fps. AMD talks about an average 12% performance increase across all applications. In games it should be 15%. So here we have a generic IPC Plus thanks to a new micro-architecture.

The first products with 3D V-cache will be offered later this year. A Raison update with this extra memory is more than possible – before you get the first Gen 4 processors.

More news from AMD on Computex 2021:

Update: AMD answers some questions about 3D V-Cache

After the keynote address we had the opportunity to speak with Samuel Nafsikar from AMD. He was able to answer some questions about the 3D V-cache.

First, AMD clarified that production of the first Raison processors with 3D V-cache will begin by the end of 2021. More details on whether or not these processors will be available in 2021 will come later. So of course there will be processors like this (based on the Gen3 architecture). Currently, the 3D V-cache is manufactured at the same configuration width as the CCD – i.e. 7 Nm, but is in optimal shape, thus achieving extreme density.

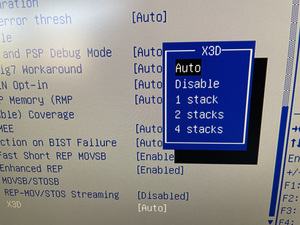

From a technical point of view, AMD clarified that this is a single layer of SRAM, so we have not yet seen the stacked SRAM, but it is stacked on the CCD. 64 MB per layer means that if AMD adds more layers here, the current version adds another 64 MB with each layer. This should be important for EPYC processors because up to four layers must be used here.

Since SRAM does not generate a lot of waste heat, the impact of temperature should be minimal. This also applies to power consumption. The L3 cache, expanded by 3D V-cache, increases the success rate on cache and may even help to minimize new access to memory. In addition, the existing Gen-3-CCD is already made of 3D V-cache and all control and power logic is in the CCD. So the 64MB V-cache can be packed at 36mm. The CCD with the 3D V-cache comes to the same height as the IoT, which is flat on the ground, and then the 3D V-cache is cast.

When asked if there were more latencies in the 3DV-case than in the CCD’s L3-cache, AMD replied that, despite the slight increase, it was moderate and could not be compared to what was visible when approaching the distance. CCD is subject to delays.

CCD’s existing L3 cache is supplemented by a 3D cache. There are no changes to the software so this temporary storage can be fixed.

“Travel maven. Beer expert. Subtly charming alcohol fan. Internet junkie. Avid bacon scholar.”

More Stories

It's better to call it a digital camera. The Xperia 1 VI lets you take any kind of photo | Gizmodo Japan

Google may be developing a new device called “Google TV Streamer” to replace “Chromecast”

What do you want to talk about? “Persona 3 Reload” recommendation campaign is running until July 31st! |.Persona Channel